Einführung

Das Linux make command ist ein häufig verwendetes Dienstprogramm von Systemadministratoren und Entwicklern. Der Befehl unterstützt den Kompilierungsprozess und ist ein unverzichtbares Tool zum Erstellen großer Anwendungen. Dieses Dienstprogramm verhindert Wiederholungen, beschleunigt die Kompilierung und spart Zeit.

Dieser Artikel zeigt Ihnen, wie Sie Linux make verwenden Befehl mit Beispielen.

Voraussetzungen

- Zugang zum Terminal.

- Die

makeFunktion installiert. - Ein Texteditor.

Hinweis: Wenn make auf dem System nicht verfügbar ist, verwenden Sie sudo apt install make .

Wie funktioniert der Make-Befehl?

Die make Der Befehl kompiliert verschiedene Programmteile und erstellt eine endgültige ausführbare Datei. Der Zweck von make besteht darin, die Dateikompilierung zu automatisieren, wodurch der Prozess einfacher und weniger zeitaufwändig wird.

Der Befehl funktioniert mit jeder Programmiersprache, solange der Compiler mit einem Shell-Befehl ausgeführt werden kann.

Das Kompilieren ist einfach, wenn Sie mit wenigen Dateien arbeiten. Daher umfasst der Prozess das Aufrufen des Compilers und das Auflisten von Dateinamen.

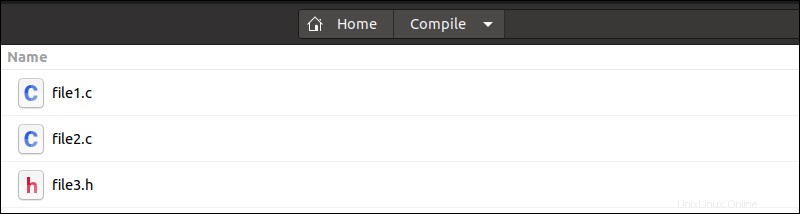

Um beispielsweise ein C-Programm aus drei Dateien zu kompilieren (file1.c , file2.c , file3.h ):

Rufen Sie den Compiler auf mit:

gcc file1.c file2.c file3.h

Die gcc Befehl erstellt ein a.out -Datei, bei der es sich um eine standardmäßig kompilierte ausführbare Datei handelt.

Das Ändern einer der Quelldateien erfordert jedoch eine Neukompilierung, was bei der Arbeit mit großen Apps noch komplizierter ist. Die make Der Befehl automatisiert den Prozess, sodass Benutzer nur Teile aktualisieren können, die geändert werden müssen, ohne jede Datei neu zu kompilieren.

Die make Der Befehl verwendet eine vom Benutzer erstellte Datei Makefile, um Programmteile zu kompilieren. Bei der ersten Ausführung make durchsucht das Makefile nach Anweisungen, z. B. Dateibeschreibungen und Änderungszeiten. Basierend auf den verfügbaren Daten, make entscheidet, welche Dateien aktualisiert werden müssen, und gibt die erforderlichen Befehle aus.

Was sind Makefiles?

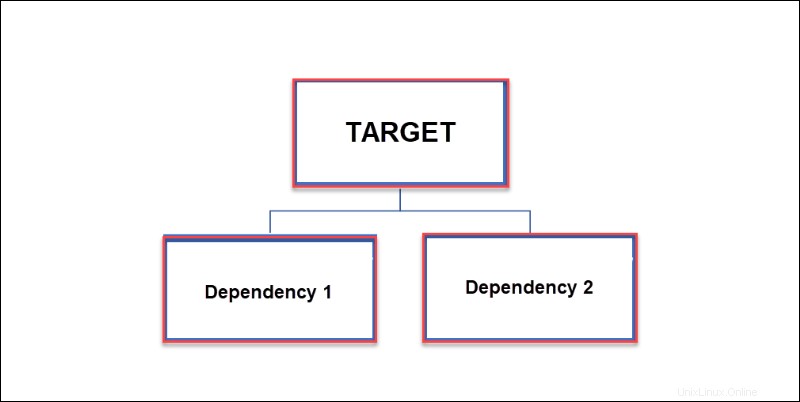

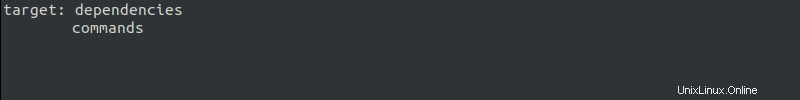

Ein Makefile ist eine Textdatei, die eine Reihe von Regeln enthält, die make anweisen wie man eine Anwendung erstellt. Eine Regel besteht aus drei Teilen:dem Ziel , Abhängigkeiten und Befehl(e) .

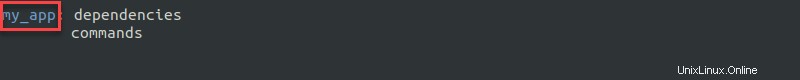

Die grundlegende Makefile-Syntax lautet:

target: dependencies

<TAB> commandsTeile der Syntax sind:

- Ziele . Namen der Dateien, die nach Ausführung von

makeerstellt oder aktualisiert werden sollen . - Abhängigkeiten . Namen der Dateien (durch Leerzeichen getrennt), aus denen das Ziel aufgebaut ist.

- Die Befehle . Regeln, die beschreiben, wie das Ziel erstellt oder aktualisiert wird, wenn sich Abhängigkeiten ändern.

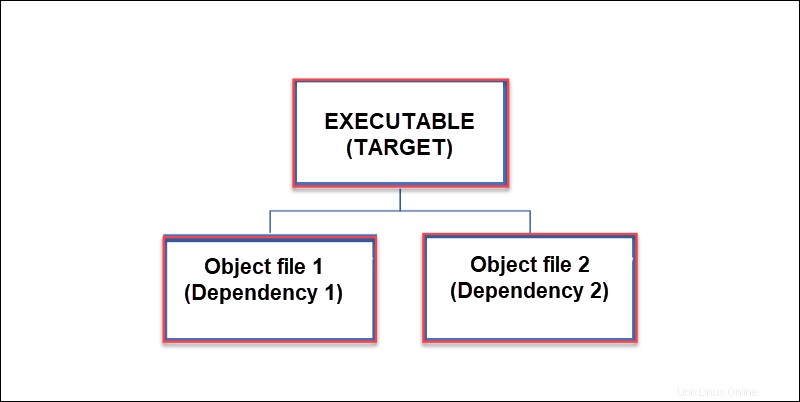

Ein Makefile hat mehrere Regelsätze. Die erste Regel ist die Standardregel und gibt an, wie die endgültige ausführbare Datei (das Ziel) aus noch nicht erstellten Objektdateien (Abhängigkeiten) erstellt werden soll:

Die Syntax lautet in diesem Fall:

EXECUTABLE: Object file 1, Object file 2

<TAB> commandsHinweis: Die Befehle in Makefiles kommen immer nach dem TAB Schlüssel. Andernfalls funktioniert der Befehl nicht.

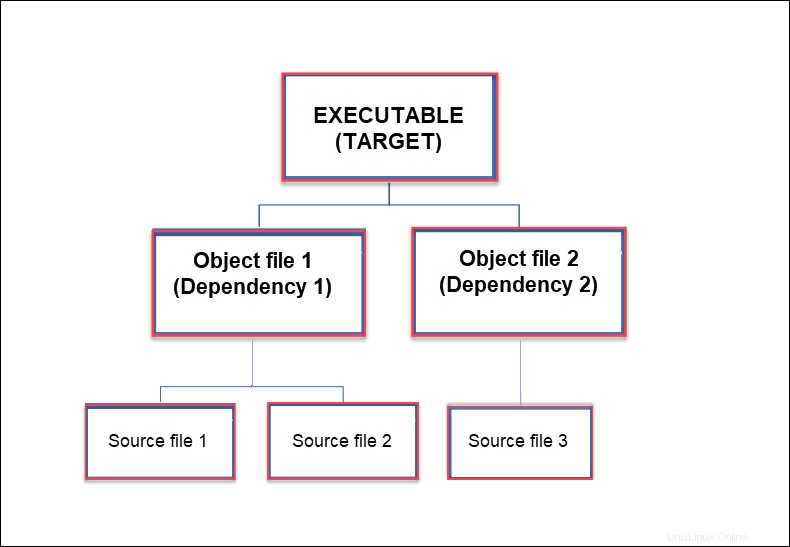

Nach dem Festlegen von Regel eins fügt der Benutzer Anweisungen zum Erstellen von Objektdateien hinzu:

Die make Der Befehl funktioniert, indem er Quelldateien in Objektdateien kompiliert und dann Objektdateien in die Zieldatei, die endgültige ausführbare Datei, kompiliert. Die Makefile-Syntax mit den drei oben genannten Regeln lautet:

EXECUTABLE: Object file 1, Object file 2

<TAB> commands

Object file 1: Source file 1, Source file 2

<TAB> commands

Object file 2: Source file 2

<TAB> commandsLinux-make-Befehlssyntax

Die grundlegenden make Syntax sieht so aus:

make [OPTIONS]

Bei Ausführung ohne Argumente make baut das erste Ziel aus dem Makefile.

Linux make Befehlsoptionen

Der make Befehl ist aufgrund seiner Effektivität, Vielfalt und der Fähigkeit, bestimmte Aktionen auszuführen, weit verbreitet. Während der Befehl das Ergebnis ausgibt, wenn er ohne Optionen ausgeführt wird, erweitert das Hinzufügen von Argumenten make 's Benutzerfreundlichkeit.

Hier sind die am häufigsten verwendeten Optionen:

| Befehl | Beschreibung |

|---|---|

-B , --always-make | Kompiliert bedingungslos alle Ziele. |

-d , --debug[=FLAGS] | Druckt die Debugging-Informationen. |

-C dir , --directory=dir | Ändert das Verzeichnis, bevor das Makefile ausgeführt wird. |

-f file , --file=file , --Makefile=FILE | Verwendet eine bestimmte Datei als Makefile. |

-i , --ignore-errors | Ignoriert alle Fehler in Befehlen. |

-I dir , --include-dir=dir | Gibt ein Verzeichnis an, in dem nach dem angegebenen Makefile gesucht werden soll. |

-j [jobs] , --jobs[=jobs] | Gibt die Anzahl der gleichzeitig auszuführenden Jobs an. |

-k , --keep-going | Führt make weiter aus so lange wie möglich, nachdem ein Fehler aufgetreten ist. |

-l [load] , --load-average[=load] | Gibt an, dass keine neue Aufgabe gestartet werden soll, wenn sich andere Aufgaben in der Warteschlange befinden. |

-n , --dry-run , --just-print , --recon | Druckt die erwartete Ausgabe, ohne make auszuführen . |

-o file , --old-file=file , --assume-old=file | Stellt sicher, dass make erstellt die Datei nicht neu, selbst wenn sie älter ist als die Abhängigkeiten. |

-p , --print-data-base | Druckt die nach dem Lesen des Makefiles erstellte Datenbank. |

-q , --question | Aktiviert den Fragemodus, in dem make führt keine Befehle aus, gibt aber einen Exit-Status null zurück, wenn das Ziel bereits kompiliert ist. |

-r , --no-builtin-rules | Beseitigt die eingebauten impliziten Regeln. |

-s , --silent , --quiet | Schränkt das Drucken der Befehle ein, während sie ausgeführt werden. |

-S , --no-keep-going , --stop | Stoppt "-k , --keep-going " Befehl. |

-t , --touch | Berührt Dateien, anstatt die Befehle auszuführen. |

--trace | Verfolgt die Disposition jedes Ziels. |

-W file , --what-if=file , --new-file=file , --assume-new=file | Ignoriert die Tatsache, dass die Zieldatei geändert wurde. |

--warn-undefined-variables | Warnt, dass auf eine unbekannte Variable verwiesen wird. |

Beispiele für make-Befehle unter Linux

Der beste Weg, um make zu verstehen und Makefiles ist durch Ausführen des Befehls und verschiedener Optionen in einem einfachen Programm.

Zum Beispiel, um eine ausführbare Datei zu erstellen, die die Nachricht "Learn about Makefiles" ausgibt , gehen Sie folgendermaßen vor:

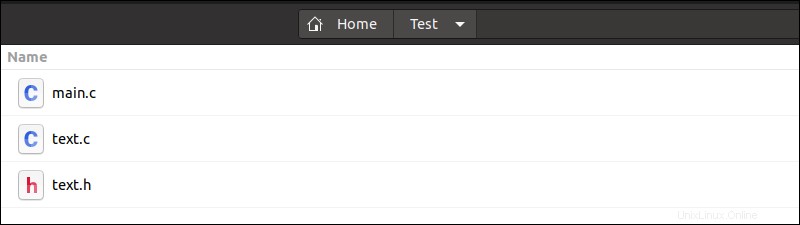

1. Erstellen Sie ein Verzeichnis namens Test .

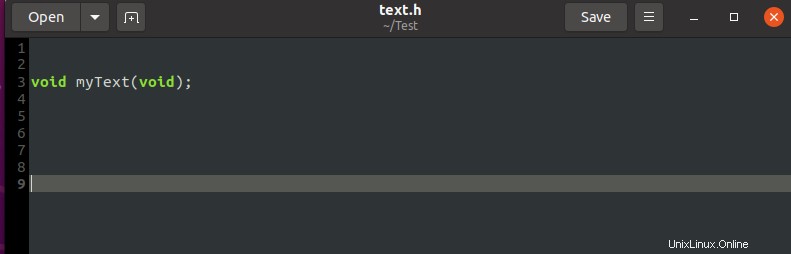

2. Erstellen Sie drei Quelldateien main.c , text.c , und text.h :

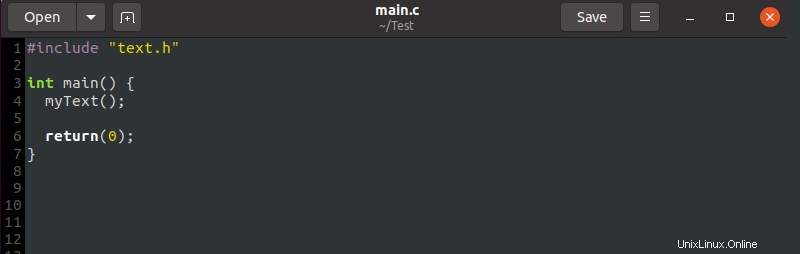

- main.c - ist die Datei mit der Hauptfunktion (

int main), die eine Funktion aus einer anderen Datei aufruft.

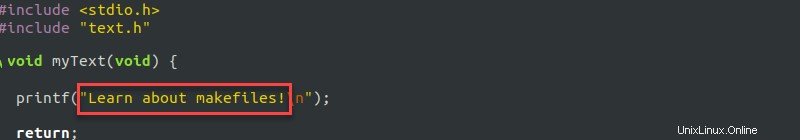

- text.c - ist die Datei mit der Sie drucken möchten "Learn about Makefiles!".

- text.h - ist die Header-Datei mit Deklarationen für die Funktionen. Der Header ist in beiden c enthalten Dateien mit dem

#include-Argument, das denselben Zweck hat wie das Kopieren/Einfügen des Inhalts der Kopfzeile.

Die folgenden Abschnitte veranschaulichen einige allgemeine Anwendungsfälle von make und Makefiles auf den drei oben genannten Dateien.

Hinweis: Die folgenden Beispiele sind in der Sprache C geschrieben.

Programm erstellen

Es gibt zwei Möglichkeiten, ein Programm zu erstellen:

- Kompilieren von Dateien auf die übliche Weise durch Aufrufen des gcc-Compilers. Diese Methode eignet sich für kleinere Programme.

- Make und Makefiles verwenden.

Erstellen Sie ein Programm mit dem gcc-Compiler

Verwenden Sie den gcc-Compiler nur für einfache Programme. Verwenden Sie andernfalls Makefiles, wenn Sie mit einer großen Anzahl von Dateien arbeiten.

So erstellen Sie ein Programm mit dem Compiler:

1. Öffnen Sie das Terminal und navigieren Sie zu dem Verzeichnis, das die Dateien enthält.

2. Rufen Sie gcc auf Compiler und geben Sie den Namen der beiden c ein Dateien. Der Header wird nicht kompiliert, da er bereits in c enthalten ist Dateien.

gcc main.c text.c

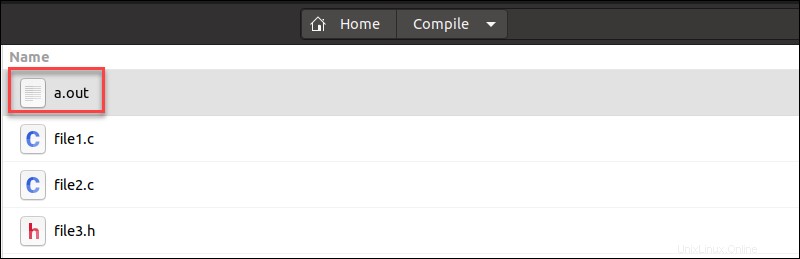

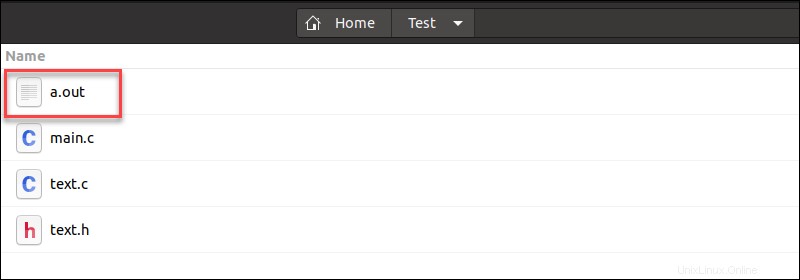

3. Listen Sie alle Dateien im aktuellen Verzeichnis mit ls auf Befehl:

ls

Das Terminal zeigt, dass die neue ausführbare Datei a.out Datei erstellt wird. Die ausführbare Datei wird auch über einen Datei-Explorer angezeigt:

Um zu testen, ob die Kompilierung erfolgreich war, rufen Sie die ausführbare Datei auf mit:

./a.out

Das Terminal zeigt, dass die ausführbare Datei ordnungsgemäß funktioniert.

Programm mit Make und Makefiles erstellen

Kompilieren von Dateien mit make und Makefiles ist einfacher als die Verwendung des Compilers. Erstellen Sie zunächst ein neues Textdokument im selben Verzeichnis und nennen Sie es Makefile oder makefile .

Öffnen Sie die Datei und verwenden Sie die grundlegende Makefile-Syntax als Richtlinie:

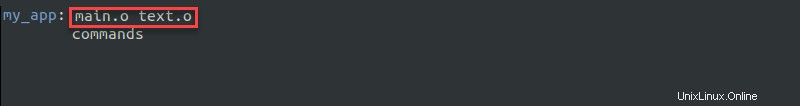

1. Geben Sie den Namen der neuen ausführbaren Datei als Ziel ein, z. B. my_app.

2. Fügen Sie die Objektdateien main.o hinzu und text.o als Abhängigkeiten. Die make Der Befehl kompiliert das Ziel jedes Mal neu, wenn sich Objektdateien ändern.

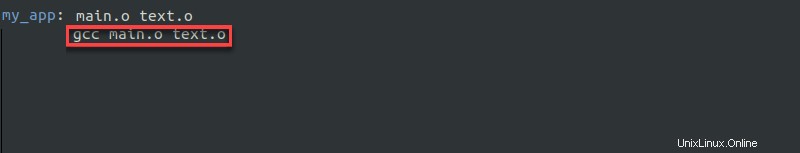

3. Drücken Sie TAB und rufen Sie gcc auf Compiler für die Objektdateien:

<TAB> gcc main.o text.o

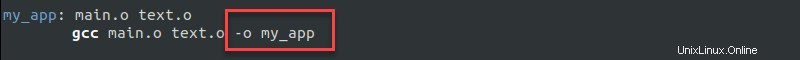

4. Fügen Sie -o hinzu Flag und nennen Sie das Ziel my_app.

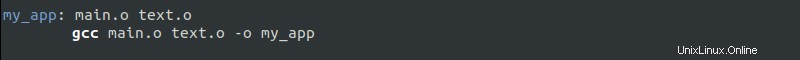

Nach dem Schreiben der ersten Regel sieht das Makefile so aus:

my_app: main.o text.o

<TAB> gcc main.o text.o -o my_app

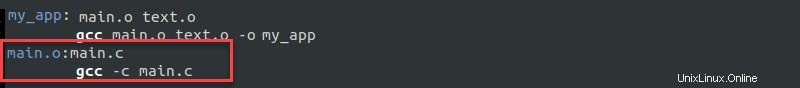

Als nächstes weisen Sie das Makefile an, wie es erstellt wird main.o :

1. Stellen Sie main.o ein als Ziel.

2. Geben Sie main.c ein als Abhängigkeit. main.c dient zum Erstellen und Aktualisieren von main.o .

3. Schreiben Sie den folgenden Befehl, um main.o zu aktualisieren jedes Mal main.c Änderungen:

gcc -c main.c

4. Fügen Sie -c hinzu Flag, um das Makefile anzuweisen, keine neue ausführbare Datei zu erstellen, sondern nur den Code zu lesen und die Objektdatei zu kompilieren.

main.o: main.c

<TAB> gcc -c main.c

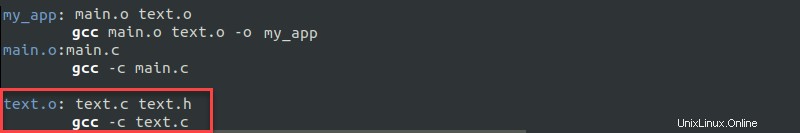

Um text.o zu erstellen , legen Sie diese Datei als Ziel fest und fügen Sie beide text.c hinzu und text.h als Abhängigkeiten. Der gcc Befehl kompiliert nur den text.c Datei, da Header niemals kompiliert werden:

text.o: text.c text.h

<TAB> gcc -c text.c

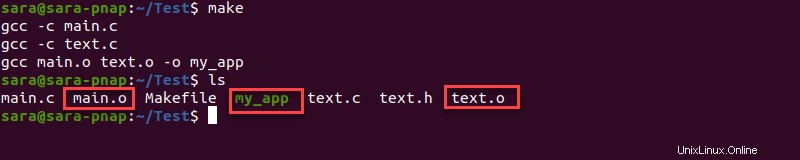

Speichern Sie das Makefile und geben Sie make ein im Terminal.

Der make Befehl zwei Objektdateien erstellt (main.o und text.o ) und die ausführbare Datei (my_app ).

Um zu überprüfen, ob make neue Dateien erstellt hat, führen Sie ls aus nochmal:

Das Terminal zeigt, dass beim Ausführen des Befehls my_app erstellt wurde . Zum Ausführen von my_app Datei, geben Sie ein:

./my_app

Programm aktualisieren

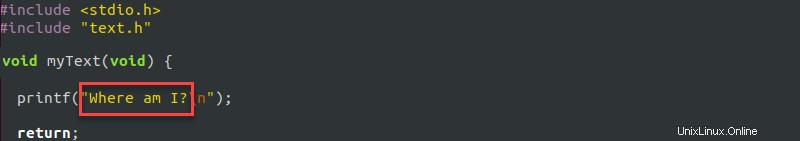

Wenn eine Quelldatei geändert wird, make aktualisiert nur Objektdateien in Abhängigkeit von dieser Quelldatei. Zum Beispiel, um den Text zu ändern, der beim Ausführen von my_app angezeigt wird von "Mehr über Makefiles erfahren “ zu „Wo bin ich ?":

1. Öffnen Sie text.c im Texteditor:

2. Ändern Sie den Text in "Wo bin ich?" :

3. Speichern Sie die Datei, öffnen Sie das Terminal und führen Sie make aus :

Die make Befehl hat Änderungen in text.c festgestellt und nur diese Datei neu kompiliert.

Um die Änderung zu überprüfen, führen Sie die ausführbare Datei aus:

./my_app

Alle Dateien kompilieren

Um alle Dateien und nicht nur die geänderten Dateien zu kompilieren, verwenden Sie -B oder --always-make Optionen.

Zum Beispiel, um den Text in der text.c zu ändern Datei zurück zu "Erfahren Sie mehr über Makefiles" und speichern Sie die Datei, geben Sie ein:

make -B

Die Ausgabe zeigt, dass make alle Dateien im Ordner kompiliert, auch die, die nicht geändert wurden.

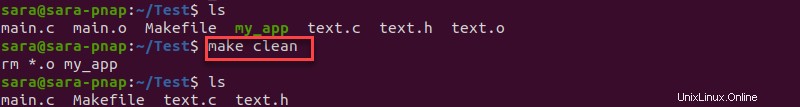

Objektdateien bereinigen

Wenn ein Benutzer make ausführt Zum ersten Mal erstellt der Befehl Objektdateien und die ausführbare Datei. Um den Quellordner zu entrümpeln und Objektdateien zu bereinigen, fügen Sie daher clean hinzu Funktion zum Makefile:

clean:

<TAB> rm *.o my_app

Der Befehl besteht aus:

- Das saubere Ziel ohne Abhängigkeiten - Das Ziel gilt immer als veraltet und wird immer ausgeführt.

- Die

rmBefehl - Entfernt bestimmte Objekte. - Der

*.oTeil - stimmt mit Dateien mit dem o überein Erweiterung und bereinigt Objektdateien und my_app .

Um Objektdateien zu bereinigen, führen Sie Folgendes aus:

make clean

Nach dem Ausführen von ls Auch hier zeigt das Terminal, dass die Objektdateien und my_app wurden entfernt.

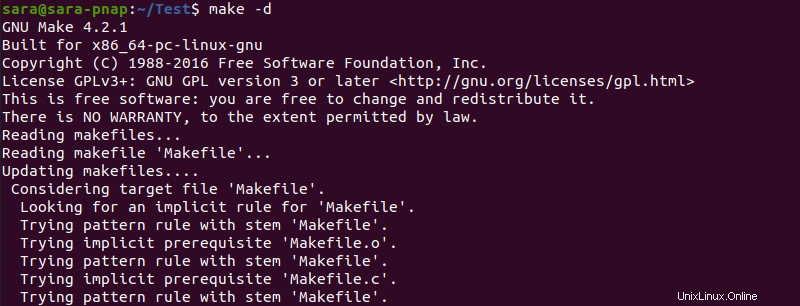

Make im Debug-Modus ausführen

Führen Sie make aus im Debug-Modus, um zusätzliche Informationen über den Kompilierungsprozess zu drucken. Führen Sie make aus mit dem -d Option zum Anzeigen der Debugging-Ausgabe:

make -d

Andere Datei als Makefile verwenden

Standardmäßig make sucht nach einer Datei namens Makefile oder makefile im aktuellen Verzeichnis. Um eine andere Datei zu verwenden, führen Sie Folgendes aus:

make -f [file_name]Beispiel:Wenn ein Makefile my_file heißt , ausführen:

make -f my_file

Variablen verwenden

Variablen in Makefiles repräsentieren mehrere Dateinamen, Argumente, Ziele, Abhängigkeiten, Befehle, Quellverzeichnisse oder andere Elemente. Außerdem wird eine Variable durch einen Namen definiert und stellt eine Textfolge dar, die als Variablenwert bezeichnet wird.

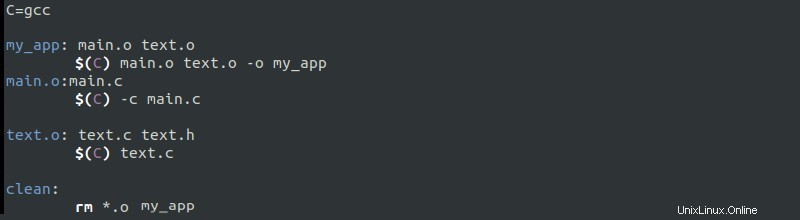

Um eine Variable zu definieren, verwenden Sie = . Ersetzen Sie beispielsweise gcc mit einer Variablen C.

C=gcc

my_app: main.o text.o

<TAB> $ (C) main.o text.o -o my_app

main.o:main.c

<TAB> $ (C) -c main.c

text.o: text.c text.h

<TAB> $ (C) -c text.c

Beim Ausführen von make im Terminal liest der Befehl den C Variable als gcc :

Fazit

Nachdem Sie die Beispiele in diesem Tutorial durchgearbeitet haben, wissen Sie, wie Sie make verwenden Befehl in Linux und wie er funktioniert.

Laden Sie als Nächstes den Spickzettel für Linux-Befehle herunter, um andere wichtige Linux-Befehle zu lernen.